2024/5/29 16:51:20

2024/5/29 16:51:20

171

171

· AC Types Feature 1.5-V to 5.5-V Operation and Balanced Noise Immunity at 30% of the Supply Voltage

· Speed of Bipolar F, AS, and S, With Significantly Reduced Power Consumption

· Designed Specifically for High-Speed Memory Decoders and Data-Transmission Systems

· Incorporates Three Enable Inputs to Simplify Cascading and/or Data Reception

· Balanced Propagation Delays

· ±24-mA Output Drive Current

– Fanout to 15 F Devices

· SCR-Latchup-Resistant CMOS Process and Circuit Design

· Exceeds 2-kV ESD Protection Per MIL-STD-883, Method 3015

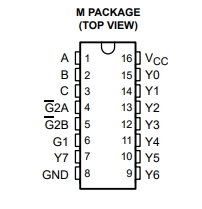

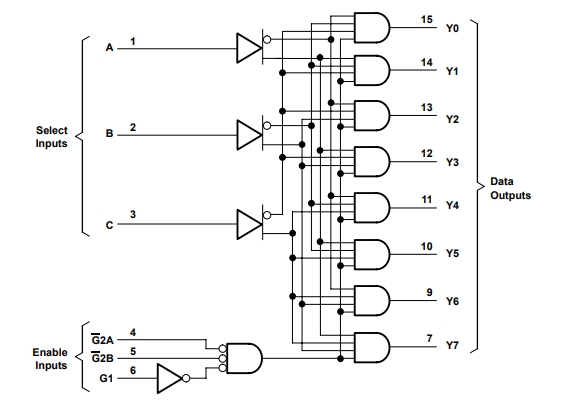

description/ordering information

The CD74AC238 decoder/demultiplexer is designed for high-performance memory-decoding and data-routing applications that require very short propagation-delay times. In high-performance memory systems, this decoder can be used to minimize the effects of system decoding. When employed with high-speed memories utilizing a fast enable circuit, the delay times of this decoder and the enable time of the memory usually are less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible.

The conditions at the binary-select inputs and the three enable inputs select one of eight output lines. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications (see Application Information).

热门型号

热门资讯

20万现货SKU

品类不断扩充

科技智能大仓储

4小时快速交货

仅从原厂和代理商进货

每一颗料均可原厂追溯

明码标价节省时间成本

一站式采购正品元器件